#### US007414600B2

### (12) United States Patent

#### Nathan et al.

## (54) PIXEL CURRENT DRIVER FOR ORGANIC LIGHT EMITTING DIODE DISPLAYS

(75) Inventors: Arokia Nathan, Waterloo (CA);

Peyman Servati, Waterloo (CA); Kapil Sakariya, Waterloo (CA); Anil Kumar,

Kitchener (CA)

(73) Assignee: **Ignis Innovation Inc.**, Waterloo, Ontario

(CA)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 311 days.

(21) Appl. No.: 11/247,455

(22) Filed: Oct. 11, 2005

(65) **Prior Publication Data**

US 2006/0027807 A1 Feb. 9, 2006

#### Related U.S. Application Data

- (63) Continuation of application No. 10/468,319, filed as application No. PCT/CA02/00173 on Feb. 18, 2002, now abandoned.

- (60) Provisional application No. 60/268,900, filed on Feb. 16, 2001.

(51) **Int. Cl. G09G** 3/32 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,996,523 A | 2/1991  | Bell et al. |

|-------------|---------|-------------|

| 5,266,515 A | 11/1993 | Robb et al. |

| 5,498,880 A | 3/1996  | Lee et al.  |

| 5,619,033 A | 4/1997  | Weisfield   |

(10) Patent No.: US 7,414,600 B2

(45) **Date of Patent:** Aug. 19, 2008

5,648,276 A 7/1997 Hara et al. 5,714,968 A 2/1998 lkeda 5,874,803 A 2/1999 Garbuzov et al.

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

CA 2242720 1/2000

#### (Continued)

#### OTHER PUBLICATIONS

Patent Abstracts of Japan vol. 1997, No. 08, Aug. 29, 1997 -& JP 09 090405 A (Sharp Corp), Apr. 4, 1997 abstract.

#### (Continued)

Primary Examiner—Patricia Nguyen (74) Attorney, Agent, or Firm—Pearne & Gordon LLP

#### (57) ABSTRACT

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed  $\Delta V_T$ -compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for  $\delta V_T$ . The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

#### 7 Claims, 13 Drawing Sheets

# US 7,414,600 B2 Page 2

| U.S. PATENT DOCUMENTS                                                   | 2006/0261841 A1* 11/2006 Fish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5,903,248 A 5/1999 lrwin                                                | FOREIGN PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 5,917,280 A 6/1999 Burrows et al.                                       | EP 1 028 471 8/2000<br>EP 1 130 565 A1 9/2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 6,023,259 A 2/2000 Howard et al.<br>6,091,203 A 7/2000 Kawashima et al. | OTHER PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 6,229,508 B1 5/2001 Kane                                                | Ma E Y et al: "Organic Light-Emitting Diode/Thin Film Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 6,246,180 B1 6/2001 Nishigaki                                           | Integration for Foldable Displays" Conference Record of the 1997 International Display Research Conference and International Workshops on LCD Technology and Emissive Technology. Toronto, Sep. 15-19, 1997, International Display Research Conference (IDRC), Santa Ana, CA, SID, US, vol. CONF. 17, Sep. 15, 1997, pp. 78-81, XP000931235 p. L-78, col. 2, last paragraph-p. L-80, col. 1, paragraph 1.  Patent Abstracts of Japan vol. 1999, No. 13, Nov. 30, 1999 -& JP 11 231805 A (Sanyo Electric Co Ltd), Aug. 27, 1999 abstract. Stewart M. et al., "Polysilicon TFT Technology for Active Matrix OLED Displays" IEEE Transactions on Electron Devices, vol. 48, |  |

| 6,252,248 B1 6/2001 Sano et al.<br>6,307,322 B1 10/2001 Dawson et al.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 6,580,408 B1 6/2003 Bae et al.                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 6,693,610 B2 * 2/2004 Shannon et al 345/76                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 7,129,914 B2 * 10/2006 Knapp et al                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 7,248,236 B2 * 7/2007 Nathan et al                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2001/0026257 A1 10/2001 Kimura                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2001/0030323 A1 10/2001 Ikeda                                           | No. 5, pp. 845-851, May 5, 2001.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2001/0045173 A1 11/2001 Troutman                                        | Nathan A et al: "Thin film technology on glass and plastic" ICM 2000. Proceedings of the 12th International Conference on Micro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2001/0045929 A1 11/2001 Prache et al.<br>2002/0000576 A1 1/2002 Inukai  | electronics. (IEEE Cat. No. 00EX453), ICM 2000. Proceedings of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 2002/0011796 A1 1/2002 Koyama                                           | the 12th International Conference on Microelectronics, Tehran, Iran, Oct. 31-Nov. 2, 2000, pp. 11-14, XP002206242 2000, Tehran, Iran,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 2002/0011799 A1 1/2002 Kimura                                           | Univ. Tehran, Iran, ISBN: 964-360-057-2, p. 13, col. 1, line 11-48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 2005/0067971 A1* 3/2005 Kane                                            | * cited by examiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

Fig. 1

transparent anode for surface

OLED

dielectric

a-Si:H

a-Si:H

gate

Glass or plastic

Fig. 17

Fig. 3

☑ glass substrate□ a-SiN<sub>x</sub>:H □ a-Si:H থ n⁺μc-Si:H ■ metal

Fig. 4

Fig. 5A

Fig. 5B

Fig. 6A

Aug. 19, 2008

Fig. 6B

**Fig.** 7

Fig. 8

Fig. 9

Fig. 10

Aug. 19, 2008

**Fig. 12**

Fig. 15

#### PIXEL CURRENT DRIVER FOR ORGANIC LIGHT EMITTING DIODE DISPLAYS

This application is a continuation application of U.S. patent application Ser. No. 10/468,319 filed Jan. 23, 2004 now abandoned, which is the U.S. National Phase of PCT/ CA02/00173 having an International Filing Date of Feb. 18, 2002, which claims the benefit of U.S. Provisional Patent Application Ser. No. 60/268,900 filed on Feb. 16, 2001.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a an organic light emitting diode display, and more particularly to an a pixel current driver for an organic light emitting display (OLED), capable of minimizing parasitic couplings between the OLED and the transistor layers.

#### 2. Description of the Prior Art

OLED displays have gained significant interest recently in display applications in view of their faster response times, larger viewing angles, higher contrast, lighter weight, lower power, amenability to flexible substrates, as compared to 25 liquid crystal displays (LCDs). Despite the OLED's demonstrated superiority over the LCD, there still remain several challenging issues related to encapsulation and lifetime, yield, color efficiency, and drive electronics, all of which are receiving considerable attention. Although passive matrix 30 addressed OLED displays are already in the marketplace, they do not support the resolution needed in the next generation displays, since high information content (HIC) formats are only possible with the active matrix addressing scheme. tronics, based on thin-film transistors (TFTs) fabricated using amorphous silicon (a-Si:H), polycrystalline silicon (poly-Si), or polymer technologies, to provide the bias voltage and drive current needed in each OLED pixel. Here, the voltage on each pixel is lower and the current throughout the entire frame 40 period is a low constant value, thus avoiding the excessive peak driving and leakage currents associated with passive matrix addressing. This in turn increases the lifetime of the

In active matrix OLED (AMOLED) displays, it is impor- 45 tant to ensure that the aperture ratio or fill factor (defined as the ratio of light emitting display area to the total pixel area) should be high enough to ensure display quality. Conventional AMOLED displays are based on light emission through an aperture on the glass substrate where the backplane elec- 50 tronics is integrated. Increasing the on-pixel density of TFT integration for stable drive current reduces the size of the aperture. The same happens when pixel sizes are scaled down. The solution to having an aperture ratio that is invariant on scaling or on-pixel integration density is to vertically stack 55 pixel driver and its associated input-output timing diagrams; the OLED layer on the backplane electronics, along with a transparent top electrode (see FIG. 2). In FIG. 2, reference numerals S and D denote a source and a drain respectively. This implies a continuous back electrode over the OLED pixel. However, this continuous back electrode can give rise 60 to parasitic capacitance, whose effects become significant when the electrode runs over the switching and other thin film transistors (TFTs). Here, the presence of the back electrode can induce a parasitic channel in TFTs giving rise to high leakage current. The leakage current is the current that flows 65 having p-channel drive TFTs; between source and drain of the TFT when the gate of the TFT is in its OFF state.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide to a pixel current driver for an organic light emitting display(OLED), capable of minimizing parasitic couplings between the OLED and the transistor layers.

In order to achieve the above object, a pixel current driver for OLED layer for emitting light according to the present invention comprises a plurality of thin film transistors (TFTs) 10 each having dual gates and for driving the OLED layer. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance.

Each of the thin film transistor may be an a-Si:H based thin 15 film transistor or a polysilicon-based thin film transistor.

The pixel current driver is a current mirror based pixel current driver for automatically compensating for shifts in the Vth of each of the thin film transistor in a pixel and the pixel current driver is for monochrome displays or for full color 20 displays.

The dual gates are fabricated in a normal inverted staggered TFT structure. A width of each of the TFTs is formed larger than a length of the same to provide enough spacing between the source and drain for the top gate. Preferably, the length is 30 µm and the width is 1600 µm. The length and width of the transistors may change depending on the maximum drive current required by the circuit and the fabrication technology used. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed  $\Delta V_T$ compensated manner, or four or The OLED layer is vertically stacked on the plurality of thin film transistors.

With the above structure of an a-Si:H current driver accord-Active matrix addressing involves a layer of backplane elec- 35 ing to the present invention, the charge induced in the top channel of the TFT is minimized, and the leakage currents in the TFT is minimized so as to enhance circuit performance.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above objects and features of the present invention will become more apparent by describing in detail preferred embodiments thereof with reference to the attached drawings in which:

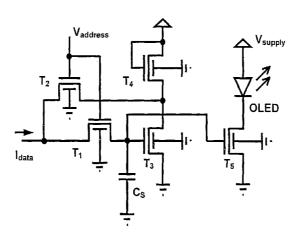

FIG. 1 shows variation of required pixel areas with mobility for 2-T and 5-T pixel drivers;

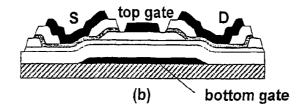

FIG. 2 shows a pixel architecture for surface emissive a-Si:H AMOLED displays;

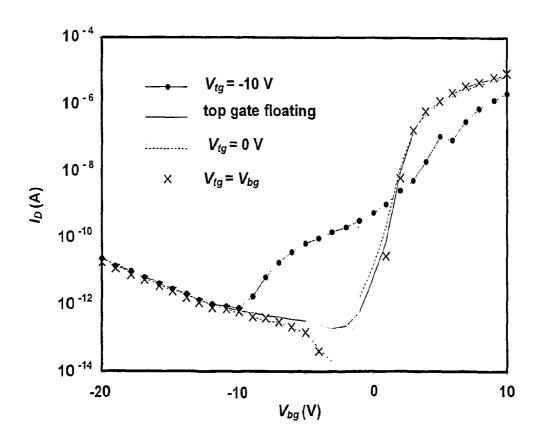

FIG. 3 shows a cross section of a dual-gate TFT structure; FIG. 4 shows forward and reverse transfer characteristics of dual-gate TFT for various top gate biases;

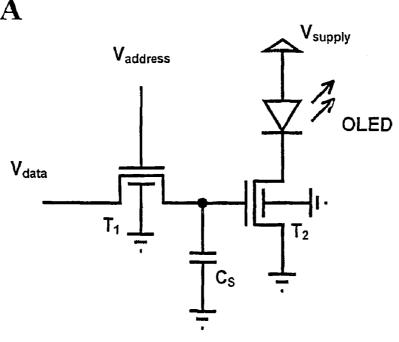

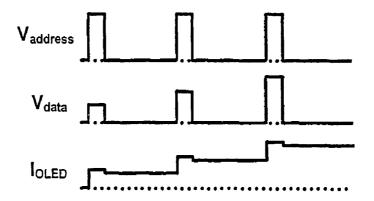

FIG. 5A and FIG. 5B show an equivalent circuit for a 2-T pixel driver and its associated input-output timing diagrams;

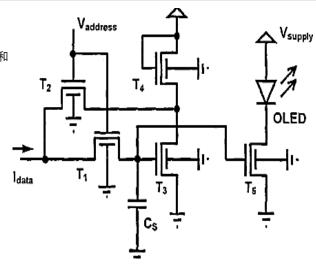

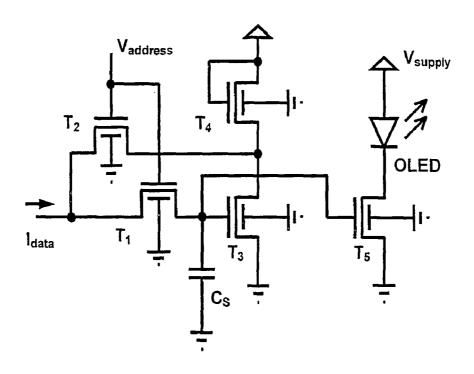

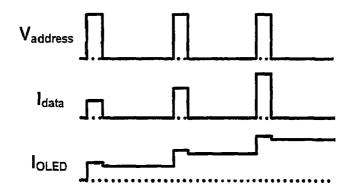

FIG. 6A and FIG. 6B show an equivalent circuit for a 5-T

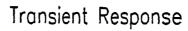

FIG. 7 shows transient performance of the 5-T driver for three consecutive write cycles;

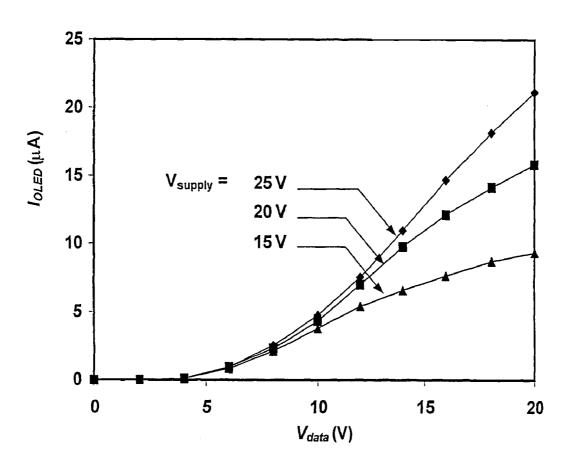

FIG. 8 shows input-output transfer characteristics for the 2-T pixel driver for different supply voltages;

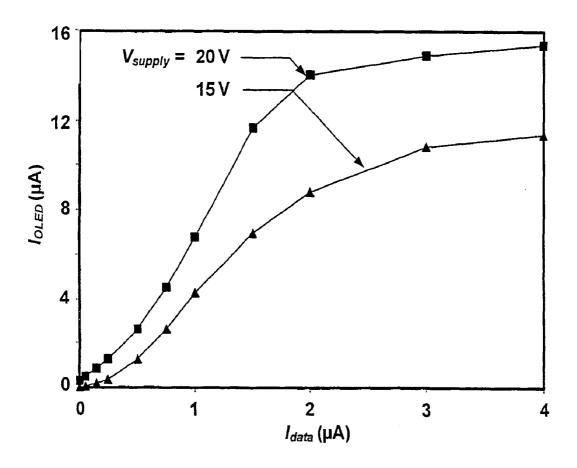

FIG. 9 shows input-output transfer characteristics for the 5-T pixel driver for different supply voltages;

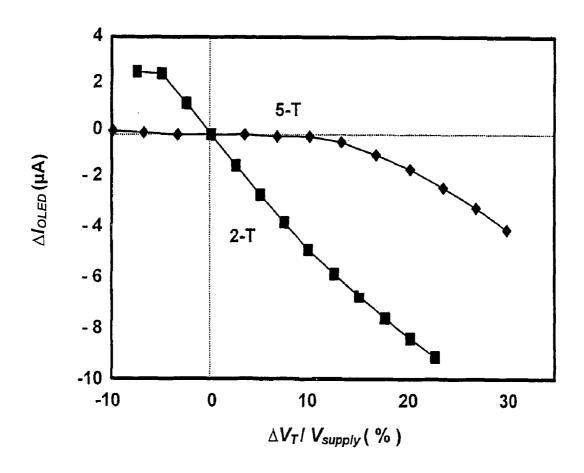

FIG. 10 shows variation in OLED current as a function of the normalized shift in threshold voltage;

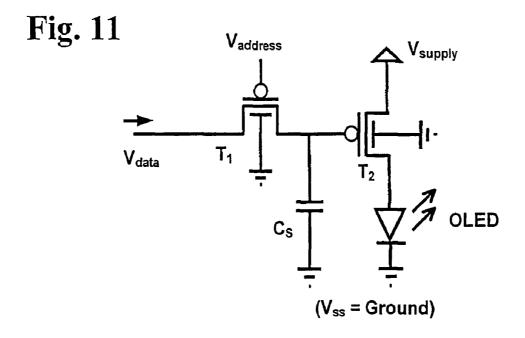

FIG. 11 shows a 2-T polysilicon based pixel current driver

FIG. 12 shows a 4-T pixel current driver for OLED dis-

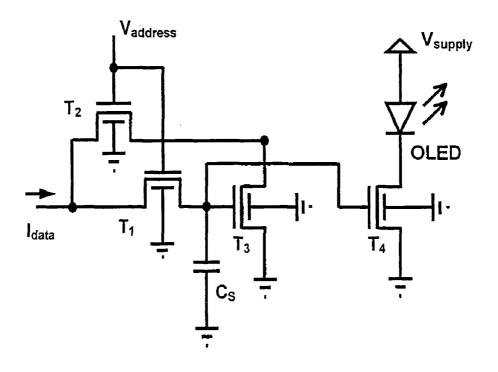

3

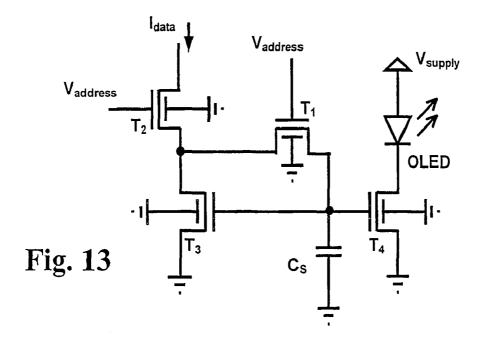

FIG. 13 shows a 4-T pixel current driver with a lower discharge time;

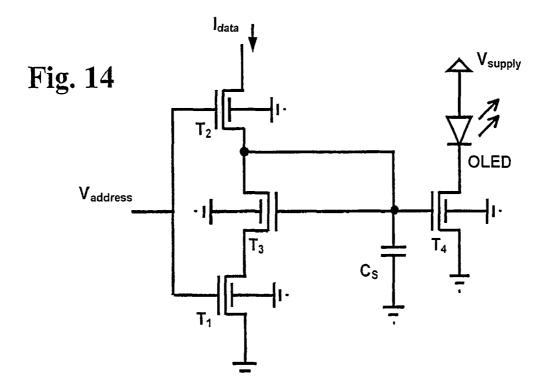

FIG. 14 shows a 4-T pixel current driver without non-linear

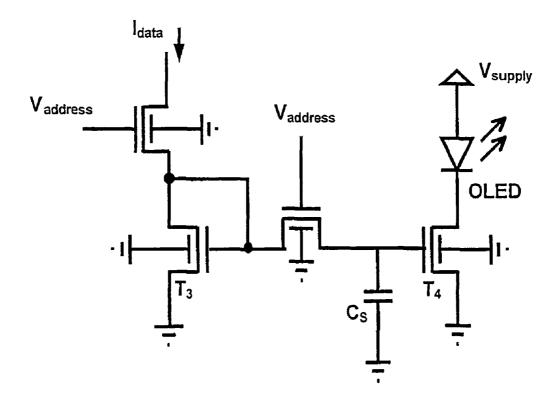

FIG. 15 shows a 4-T pixel current driver that is the building block for the full color circuit;

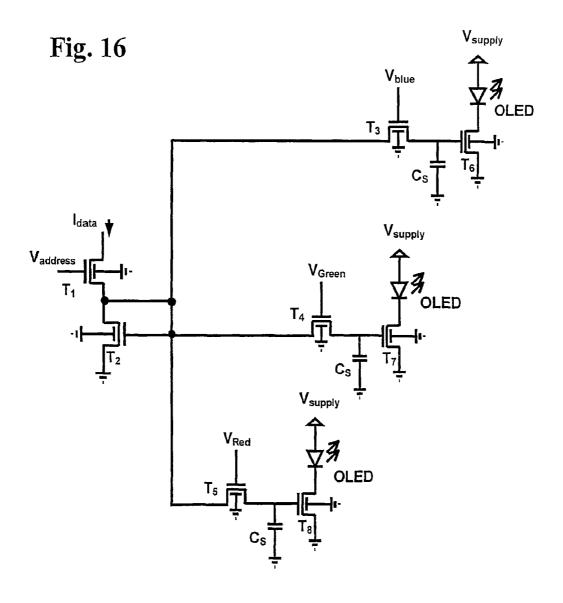

FIG. 16 shows a full color(RGB) pixel current driver for OLED displays; and

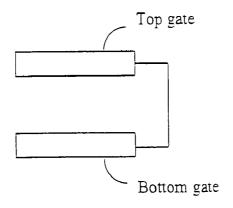

FIG. 17 shows a schematic diagram of the top gate and the bottom gate of a dual gate transistor where the top gate is electrically connected to the bottom gate.

#### DETAILED DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Although amorphous Si does not enjoy equivalent electronic properties compared to poly-Si, it adequately meets many of the drive requirements for small area displays such as those needed in pagers, cell phones, and other mobile devices. 20 Poly-Si TFTs have one key advantage in that they are able to provide better pixel drive capability because of their higher mobility, which can be of the order of  $\mu_{FE}$ ~100 cm<sup>2</sup>/Vs. This makes poly-Si highly desirable for large area (e.g. laptop size) VGA and SVGA displays. The lower mobility associated 25 with a-Si:H TFTs ( $\mu_{FE}$ ~1 cm<sup>2</sup>/Vs) is not a limiting factor since the drive transistor in the pixel can be scaled up in area to provide the needed drive current. The OLED drive current density is typically 10 mA/cm<sup>2</sup> at 10V operation to provide a brightness of 100 cd/m<sup>2</sup>—the required luminance for most 30 displays. For example, with an a-Si:H TFT mobility of 0.5 cm<sup>2</sup>/Vs and channel length of 25 μm, this drive current requirement translates into required pixel area of 300 μm<sup>2</sup>, which adequately meets the requirements of pixel resolution and speed for some 3 inch monochrome display applications. 35 FIG. 1 illustrates simulation results for the variation of the required pixel size with device mobility calculated for two types of drivers, which will be elaborated later, the 2-T and the 5-T drivers, wherein  $\mu_0$  denotes a reference mobility whose value is in the range 0.1 to  $1 \text{ cm}^2/\text{Vs}$ . For instance, the  $_{40}$ area of the pixel for the 2-T driver (see FIG. 5A) comprises of the area of the switching transistors, area of the drive transistor, and the area occupied by interconnects, bias lines, etc. In FIG. 1, the drive current and frame rate are kept constant at 10  $\mu$ A and 50 Hz, respectively, for a 230×230 array. It is clear that  $_{45}$ there is no significant savings in area between the 2-T and 5-T drivers but the savings are considerable with increasing mobility. This stems mainly from the reduction in the area of the drive transistor where there is a trade-off between  $\mu_{FF}$  and TFT aspect ratio, W/L (Wide/Length).

In terms of threshold voltage  $(V_T)$  uniformity and stability, both poly-Si and a-Si:H share the same concerns, although in comparison, the latter provides for better spatial uniformity but not stability  $(\Delta V_T)$ . Thus the inter-pixel variation in the circuit design techniques can be employed to compensate for  $\Delta V_T$  hence improving drive current uniformity. In terms of long term reliability, it is not quite clear with poly-Si technology, although there are already products based on a-Si:H technology for displays and imaging, although the reliability 60 issues associated with OLEDs may yet be different. The fabrication processes associated with a-Si:H technology are standard and adapted from mainstream integrated circuit (IC) technology, but with capital equipment costs that are much lower. One of the main advantages of the a-Si:H technology is 65 that it has become low cost and well-established technology, while poly-Si has yet to reach the stage of manufacturability.

The technology also holds great promise for futuristic applications since good as deposited a-Si:H, a-SiN<sub>x</sub>:H, and TFT arrays can be achieved at low temperatures (≦120° C.) thus making it amenable to plastic substrates, which is a critical requirement for mechanically flexible displays.

To minimize the conduction induced in all TFTs in the pixel by the back electrode, an alternate TFT structure based on a dual-gate structure is employed. In a dual gate TFT (see FIG. 3), a top gate electrode is added to the TFT structure to prevent the OLED electrodes from biasing the a-Si:H channel area (refer to FIG. 2). The voltage on the top gate can be chosen such so as to minimize the charge induced in the (parasitic) top channel of the TFT. The objective underlying the choice of the voltage on the top gate is to minimize parasitic capacitance in the driver circuits and leakage currents in the TFTs so as to enhance circuit performance. In what follows, the operation of the dual-gate TFT is described, which will be central to surface emissive (100% aperture ratio) AMOLED displays based on a-Si:H backplane electronics.

FIG. 3 illustrates the structure of a dual-gate TFT fabricated for this purpose, wherein reference numerals S and D denote a source and a drain respectively. The fabrication steps are the same as of that of a normal inverted staggered TFT structure except that it requires a sixth mask for patterning the top gate. The length of the TFT is around 30 µm to provide enough spacing between the source and drain for the top gate, and the width is made very large (1600 µm) with four of these TFTs are interconnected in parallel to create a sizeable leakage current for measurement. A delay time is inserted in the measurement of the current to ensure that the measurement has passed the transient period created by defects in the a-Si:H active layer, which give rise to a time-dependent capacitance.

FIG. 4 shows results of static current measurements for four cases: first when the top gate is tied to -10V, second when the top gate is grounded, third when the top gate is floating, and lastly when the top gate is shorted to the bottom gate. With a floating top gate, the characteristics are almost similar to that of a normal single gate TFT. The leakage current is relatively high particularly when the top gate is biased with a negative voltage. The lowest values of leakage current are obtained when the top gate is pegged to either 0V or to the voltage of the bottom gate. In particular, with the latter the performance of the TFT in the (forward) sub-threshold regime of operation is significantly improved. This enhancement in sub-threshold performance can be explained by the forced shift of the effective conduction path away from the bottom interface to the bulk a-Si:H region due to the positive bias on the top gate. This in turn decreases the effect of the trap states at the bottom interface on the sub-threshold slope of the TFT.

It should be noted that although the addition of another drive current can be a concern in both cases, although clever 55 metal contact as the top gate reduces the leakage current of the TFT, it can potentially degrade pixel circuit performance by possible parasitic capacitances introduced by vertically stacking the OLED pixel. Thus the choice of top gate connection becomes extremely critical. For example, if the top gates in the pixel circuit are connected to the bottom gates of the associated TFTs, this gives rise to parasitic capacitances located between the gates and the cathode, which can lead to undesirable display operation (due to the charging up of the parasitic capacitance) when the multiplexer O/P drives the TFT switch. On the other hand, if the top gates are grounded, this results in the parasitic capacitance being grounded to yield reliable and stable circuit operation.

5

The OLED drive circuits considered here are the wellknown voltage-programmed 2-T driver and the more sophisticated current-programmed  $\Delta V_T$ -compensated 5-T version (see FIGS. 5A and 6A). The latter is a significant variation of the previous designs, leading to reduced pixel area (<300 μm), reduced leakage, lower supply voltage (20V), higher linearity (~30 db), and larger dynamic range (~40 dB). Before dwelling on the operation of the 5-T driver, the operation of the relatively simple voltage-driven 2-T driver is described. FIG. 5B shows input-output timing diagrams of the 2-T pixel driver. When the address line is activated, the voltage on the data line starts charging capacitor C<sub>S</sub> and the gate capacitance of the driver transistor T<sub>2</sub>. Depending on the voltage on the data line, the capacitor charges up to turn the driver transistor T<sub>2</sub> on, which then starts conducting to drive the OLED with 15 the appropriate level of current. When the address line is turned off,  $T_1$  is turned off but the voltage at the gate of  $T_2$ remains since the leakage current of T<sub>1</sub> is trivial in comparison. Hence, the current through the OLED remains unchanged after the turn off process. The OLED current 20 changes only the next time around when a different voltage is written into the pixel.

Unlike the previous driver, the data that is written into the 5-T pixel in this case is a current (see FIG. 6A). FIG. 6B shows input-output timing diagrams of a 5-T pixel driver. The 25 address line voltage,  $V_{address}$  and  $I_{data}$  are activated or deactivated simultaneously. When  $V_{address}$  is activated, it forces  $T_1$  and  $T_2$  to turn on.  $T_1$  immediately starts conducting but  $T_2$ does not since T<sub>3</sub> and T<sub>4</sub> are off. Therefore, the voltages at the drain and source of T<sub>2</sub> become equal. The current flow 30 through  $T_1$  starts charging the gate capacitor of transistors  $T_3$ and  $T_5$ , very much like the 2-T driver. The current of these transistors start increasing and consequently T2 starts to conduct current. Therefore, T<sub>1</sub>'s share of I<sub>data</sub> reduces and T<sub>2</sub>'s share of  $I_{data}$  increases. This process continues until the gate 35 capacitors of  $T_3$  and  $T_5$  charge (via  $T_1$ ) to a voltage that forces the current of  $T_3$  to be  $I_{data}$ . At this time, the current of  $T_1$  is zero and the entire  $I_{data}$  goes through  $T_2$  and  $T_3$ . At the same time, T<sub>5</sub> drives a current through the OLED, which is ideally equal to  $I_{data}^*(W_5/W_3)$ , which signifies a current gain. Now if 40  $I_{data}$  and  $V_{address}$  are deactivated,  $T_2$  will turn off, but due to the presence of capacitances in  $T_3$  and  $T_5$ , the current of these two devices cannot be changed easily, since the capacitances keep the bias voltages constant. This forces T<sub>4</sub> to conduct the same current as that of  $T_3$ , to enable the driver  $T_5$  to drive the 45 same current into the OLED even when the write period is over. Writing a new value into the pixel then changes the current driven into the OLED.

The result of transient simulation for the 5-T driver circuit is shown in FIG. 7. As can be seen, the circuit has a write time 50 of <70 µs, which is acceptable for most applications. The 5-T driver circuit does not increase the required pixel size significantly (see FIG. 1) since the sizes of T2, T3, and T4 are scaled down. This also provides an internal gain (W<sub>5</sub>/W<sub>3</sub>=8), which reduces the required input current to <2 µA for 10 µA OLED 55 current. The transfer characteristics for the 2-T and 5-T driver circuits are illustrated in FIGS. 8 and 9, respectively, generated using reliable physically-based TFT models for both forward and reverse regimes. A much improved linearity (~30 dB) in the transfer characteristics ( $I_{data}/I_{OLED}$ ) is observed for 60 the 5-T driver circuit due to the geometrically-defined internal pixel gain as compared to similar designs. In addition, there are two components (OLED and  $T_5$ ) in the high current path, which in turn decreases the required supply voltage and hence improves the dynamic range. According to FIG. 9, a 65 good dynamic range (~40 dB) is observed for supply voltage of 20V and drive currents in the range  $I_{OLED} \le 10 \,\mu\text{A}$ , which

6

is realistic for high brightness. FIG. 10 illustrates variation in the OLED current with the shift in threshold voltage for the 2-T and 5-T driver circuits. The 5-T driver circuit-compensates for the shift in threshold voltage particularly when the shift is smaller than 10% of the supply voltage. This is because the 5-T driver circuit is current-programmed. In contrast, the OLED current in the 2-T circuit changes significantly with a shift in threshold voltage. The 5-T driver circuit described here operates at much lower supply voltages, has a much larger drive current, and occupies less area.

The pixel architectures are compatible to surface (top) emissive AMOLED displays that enables high on-pixel TFT integration density for uniformity in OLED drive current and high aperture ratio. A 5-T driver circuit has been described that provides on-pixel gain, high linearity (~30 dB), and high dynamic range (~40 dB) at low supply voltages (15-20V) compared to the similar designs (27V). The results described here illustrate the feasibility of using a-Si:H for 3-inch mobile monochrome display applications on both glass and plastic substrates. With the latter, although the mobility of the TFT is lower, the size of the drive transistor can be scaled up yet meeting the requirements on pixel area as depicted in FIG. 1.

Polysilicon has higher electron and hole mobilities than amorphous silicon. The hole mobilities are large enough to allow the fabrication of p-channel TFTs.

The advantage of having p-channel TFTs is that bottom emissive OLEDs can be used along with a p-channel drive TFT to make a very good current source. One such circuit is shown in FIG. 11. In FIG. 11, the source of the p-type drive TFT is connected to Vdd. Therefore, Vgs, gate-to-source voltage, and hence the drive current of the p-type TFT is independent of OLED characteristics. In other words, the driver shown in FIG. 11 performs as a good current source. Hence, bottom emissive OLEDs are suitable for use with p-channel drive TFTs, and top emissive OLEDs are suitable for use with n-channel TFTs.

The trade-off with using polysilicon is that the process of making polysilicon TFTs requires much higher temperatures than that of amorphous silicon. This high temperature processing requirement greatly increases the cost, and is not amenable to plastic substrates. Moreover, polysilicon technology is not as mature and widely available as amorphous silicon. In contrast, amorphous silicon is a well-established technology currently used in liquid crystal displays (LCDs). It is due to these reasons that amorphous silicon combined with top emissive OLED based circuit designs is most promising for AMOLED displays.

Compared to polysilicon TFTs, amorphous silicon TFTs are n-type and thus are more suitable for top emission circuits as shown in FIG. 2. However, amorphous silicon TFTs have inherent stability problems due to the material structure. In amorphous silicon circuit design, the biggest hurdle is the increase in threshold voltage  $V_{th}$  after prolonged gate bias. This shift is particularly evident in the drive TFT of an OLED display pixel. This drive TFT is always in the 'ON' state, in which there is a positive voltage at its gate. As a result, its  $V_{th}$  increases and the drive current decreases based on the current-voltage equation below:

$$Ids = (\mu C_{OX}W/2L)(V_{gs} - V_{th})^2 \qquad \qquad (\text{in Saturation region})$$

In the display, this would mean that the brightness of the OLED would decrease over time, which is unacceptable. Hence, the 2-T circuits shown earlier are not practical for OLED displays as they do not compensate for any increase in  $V_{\it th}$ .

7

The first current mirror based pixel driver circuit is presented, which automatically compensated for shifts in the  $V_{th}$  of the drive TFT in a pixel. This circuit is the 5-T circuit shown in FIG. 6A.

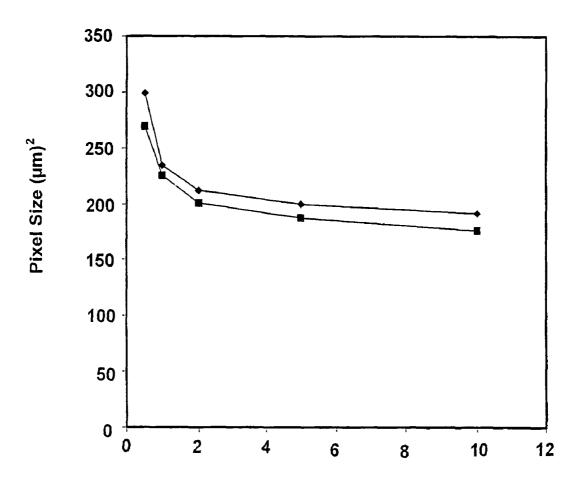

Four more OLED pixel driver circuits are presented for 5 monochrome displays, and one circuit for full colour displays. All these circuits have mechanisms that automatically compensate for  $V_{th}$  shift. The first circuit shown in FIG. 12 is a modification of the 5-T circuit of FIG. 6A. (Transistor  $T_4$  has been removed from the 5-T circuit). This circuit occupies a 10 smaller area than the 5-T circuit, and provides a higher dynamic range. The higher dynamic range allows for a larger signal swing at the input, which means that the OLED brightness can be adjusted over a larger range.

FIG. 12 shows a 4-T pixel driver circuit for OLED displays. 15 The circuit shown in FIG. 13 is a 4-T pixel driver circuit based on a current mirror. The advantage of this circuit is that the discharge time of the capacitor Cs is substantially reduced. This is because the discharge path has two TFTs (as compared to three TFTs in the circuit of FIG. 12). The charging time 20 remains the same. The other advantage is that there is an additional gain provided by this circuit because T<sub>3</sub> and T<sub>4</sub> do not have the same source voltages. However, this gain is non-linear and may not be desirable in some cases.

In FIG. 14, another 4-T circuit is shown. This circuit does 25 not have the non-linear gain present in the previous circuit (FIG. 13) since the source terminals of  $T_3$  and  $T_4$  are at the same voltage. It still maintains the lower capacitance discharge time, along with the other features of the circuit of FIG. 8.

FIG. 15 shows another version of the 4-T circuit. This circuit is does not have good current mirror properties. However, this circuit forms the building block for the 3 colour RGB circuit shown in FIG. 16. It also has a low capacitance discharge time and high dynamic range.

The full colour circuit shown in FIG. 16 minimizes the area required by an RGB pixel on a display, while maintaining the desirable features like threshold voltage shift compensation, in-pixel current gain, low capacitance discharge time, and high dynamic range.

It is important to note that the dual-gate TFTs are used in the above-mentioned circuits to enable vertical integration of the OLED layers with minimum parasitic effects. But nevertheless the circuit compensates for the Vth shift even if the simple single-gate TFTs. In addition, these circuits use n-type 45 amorphous silicon TFTs. However, the circuits are applicable to polysilicon technology using p-type or n-type TFTs. These circuits when made in polysilicon can compensate for the non-uniformity of the threshold voltage, which is a problem

8

in this technology. The p-type circuits are conjugates of the above-mentioned circuits and are suitable for the bottom emissive pixels.

We claim:

1. A pixel current driver for an organic light emitting diode (OLED) having an OLED layer for emitting light, comprising:

an address line;

a data line; and

- a plurality of thin film transistors (TFTs) forming a current mirror, each having dual gates and driving for the OLED layer, the plurality of thin film transistors comprising:

- a switch thin film transistor, a first node of the switch transistor being connected to the data line and a first gate of the dual gates of the switch transistor being connected to the address line;

- a feedback thin film transistor, a first node of the feedback transistor being connected to the data line and a first gate of the dual gates of the feedback transistor being connected to the address line;

- a reference thin film transistor, a drain of the reference transistor being connected to a second node of the feedback transistor, a first gate of the dual gates of the reference transistor being connected to a second node of the switch transistor and a source of the reference transistor being connected to a ground potential; and

- a drive thin film transistor, a first gate of the dual gates of the drive transistor being connected to the gate of the reference transistor,

- a second gate of the dual gates of each thin film transistor being formed between a back electrode of the organic light emitting diode and the first gate of the respective thin film transistor.

- 2. The pixel current driver according to claim 1 wherein the thin film transistors are amorphous silicon.

- 3. The pixel current driver according to claim 1 wherein the thin film transistors are polycrystalline silicon.

- **4**. The pixel current driver according to claim **3**, wherein each of the transistors is a p-channel thin film transistor.

- 5. The pixel current driver according to claim 1, wherein the dual gates are fabricated in a normal inverted staggered TFT structure.

- **6**. The pixel current driver according to claim **1**, wherein the second gate of the thin film transistor is grounded.

- 7. The pixel current driver according to claim 1, wherein the second gate of the thin film transistor is electrically tied to the first gate of the thin film transistor.

\* \* \* \* \*

| 专利名称(译)        | 用于有机发光二极管显示器的像素电流驱动器                                                                              |         |            |

|----------------|---------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | <u>US7414600</u>                                                                                  | 公开(公告)日 | 2008-08-19 |

| 申请号            | US11/247455                                                                                       | 申请日     | 2005-10-11 |

| [标]申请(专利权)人(译) | NATHAN AROKIA<br>SERVATI PEYMAN<br>SAKARIYA卡皮尔                                                    |         |            |

| 申请(专利权)人(译)    | NATHAN AROKIA<br>SERVATI PEYMAN<br>SAKARIYA卡皮尔                                                    |         |            |

| 当前申请(专利权)人(译)  | IGNIS创新INC.                                                                                       |         |            |

| [标]发明人         | NATHAN AROKIA<br>SERVATI PEYMAN<br>SAKARIYA KAPIL<br>KUMAR ANIL                                   |         |            |

| 发明人            | NATHAN, AROKIA<br>SERVATI, PEYMAN<br>SAKARIYA, KAPIL<br>KUMAR, ANIL                               |         |            |

| IPC分类号         | G09G3/32 H01L51/50 G09F9/30 G09G3/20 G09G3/30 H01L21/336 H01L27/12 H01L27/15 H01L27/32 H01L29/786 |         |            |

| CPC分类号         | G09G3/3233 G09G3/3241 H01L27/3276 G09G2300/0804 H01L27/12 H01L27/283 G09G2320/0223                |         |            |

| 优先权            | PCT/CA2002/000173 2002-02-18 WO<br>60/268900 2001-02-16 US<br>10/468319 2004-01-23 US             |         |            |

| 其他公开文献         | US20060027807A1                                                                                   |         |            |

| 外部链接           | Espacenet USPTO                                                                                   |         |            |

#### 摘要(译)

像素电流驱动器包括多个薄膜晶体管(TFT),每个薄膜晶体管具有双栅极并用于驱动OLED层。双栅极的顶栅形成在每个薄膜晶体管的源极和漏极之间,从而最小化寄生电容。顶栅接地或电连接到底栅。多个薄膜晶体管可以是以电压编程方式形成的两个薄膜晶体管,或者是以电流编程的ΔVT补偿方式形成的五个薄膜晶体管。还提供了具有不同数量的薄膜晶体管的其他版本的电流编程电路,其补偿δVT。 OLED层连续且垂直地堆叠在多个薄膜晶体管上,以提供接近100%的孔径比。